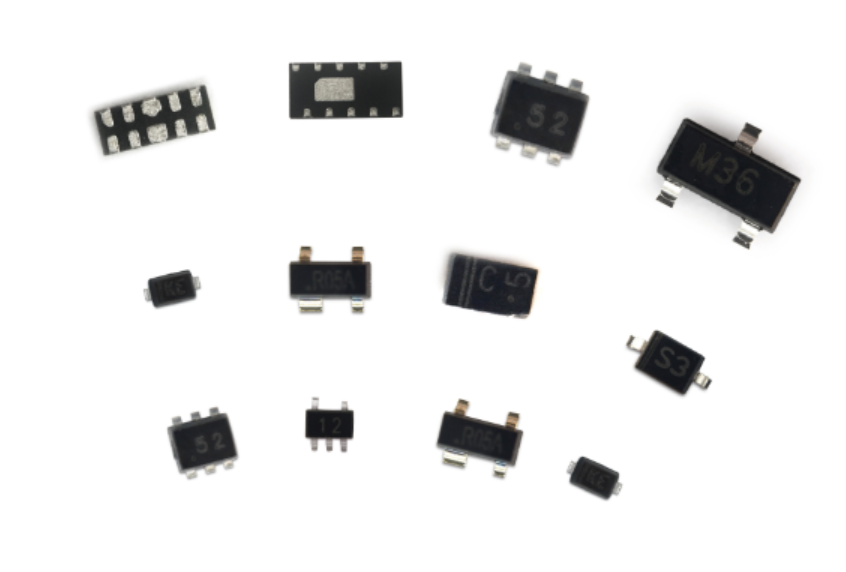

The JEDEC requirement of up to 30 KV is set because it represents a common electrostatic discharge (ESD) voltage threshold.

ESD refers to the static discharge that occurs between two objects, which can damage electronic devices or cause data loss. Therefore, to ensure the reliability and stability of devices, JEDEC established the 30 KV electrostatic discharge standard. This standard is based on practical testing and empirical data, ensuring that devices are not subjected to unacceptable ESD effects during normal operation and use.

JEDEC has developed several standards for electrostatic discharge (ESD) in electronic chips, primarily the following standard numbers:

These standards define the conditions, equipment, and test procedures for ESD testing to ensure that chips can operate safely during ESD events. Each standard addresses different ESD voltage models and specifies distinct test methods and parameters.

Hot News

Hot News