Article Source | Yuanchuan Technology Review

Author | He Luheng

TOB, Still a hot spot in the primary market.

In July 2019, Pingtouge, a semiconductor company under Alibaba, officially released the Xuantie 910, with the slogan of "one of the strongest RISC-V processors in the industry", claiming to have performance comparable to the Arm v8 architecture Cortex A7X series.

The onlookers cheered and asked each other, 'What is RISC-V?'?

The essence of a CPU is a chip that integrates different functional circuits. To use these functional circuits, the CPU needs to call the corresponding instructions, which are binary numbers composed of 0s and 1s. The thing used to specify instruction formats is called instruction set architecture (commonly referred to as architecture), and different architectures reflect designers' different implementation ideas for the same function. RISC-V is one of the top three instruction set architectures in the world.

However, these 'top three in the world' are full of moisture. In the other two instruction sets, the x86 architecture led by Intel is applied to the vast majority of PCs and servers; The Arm architecture of British company Arm is used in over 99% of smartphones worldwide.

In contrast, although RISC-V ranks closely behind, its actual share is still a fraction of the top two.

And these three architectures respectively represent three business models:

The x86 architecture is firmly controlled by Intel and AMD, and other chip companies cannot use it even if they want to;

Although the Arm architecture is owned by Arm Corporation, it is licensed and open, requiring payment for purchase;

RISC-V is the most unique and does not belong to any institution or country. It is open source and free, and can be used whenever you want. The operating costs are all supported by the brothers of the foundation.

In this context, the significance of RISC-V for Chinese companies in 2019 is not difficult to understand.

At that time, the domestic semiconductor industry was experiencing sanctions for the first time, and the RISC-V Foundation happened to relocate its headquarters from the United States to neutral Switzerland, due to concerns about possible geopolitical damage. Its free and open-source nature meant that no one could use "national security" as an excuse to restrict others from using RISC-V.

At the beginning of RISC-V's establishment, the only Chinese members of the Foundation were Alibaba, Huawei and the Institute of Computing of the Chinese Academy of Sciences. By 2022, chip enterprises in Chinese Mainland will occupy 12 seats among the 19 senior members of the Foundation.

The spring breeze is like a drum, urging the RISC-V spare tire to turn positive. However, four years have passed, and RISC-V still seems to have not overcome the dilemma of a spare tire.

Qualified spare tire

Among the three major instruction sets, x86 adopts the Complex Instruction Set Architecture (CISC), while Arm and RISC-V adopt the Reduced Instruction Set Architecture (RISC). The difference between the two, as the name suggests:

CISC strives to complete tasks in one go, which is efficient but time-consuming (high performance, high power consumption), while RISC breaks down tasks and completes them in stages. Although it does not require high personal abilities (low performance, low power consumption), the cost is lower efficiency.

In 1985, the British company Acon developed the Arm architecture, coinciding with Apple's self-developed chips. The two sides hit it off immediately, and Arm was born. Unexpectedly, it took almost 20 years for Arm architecture to emerge in the mobile processor market with the A-series chip of iPhone.

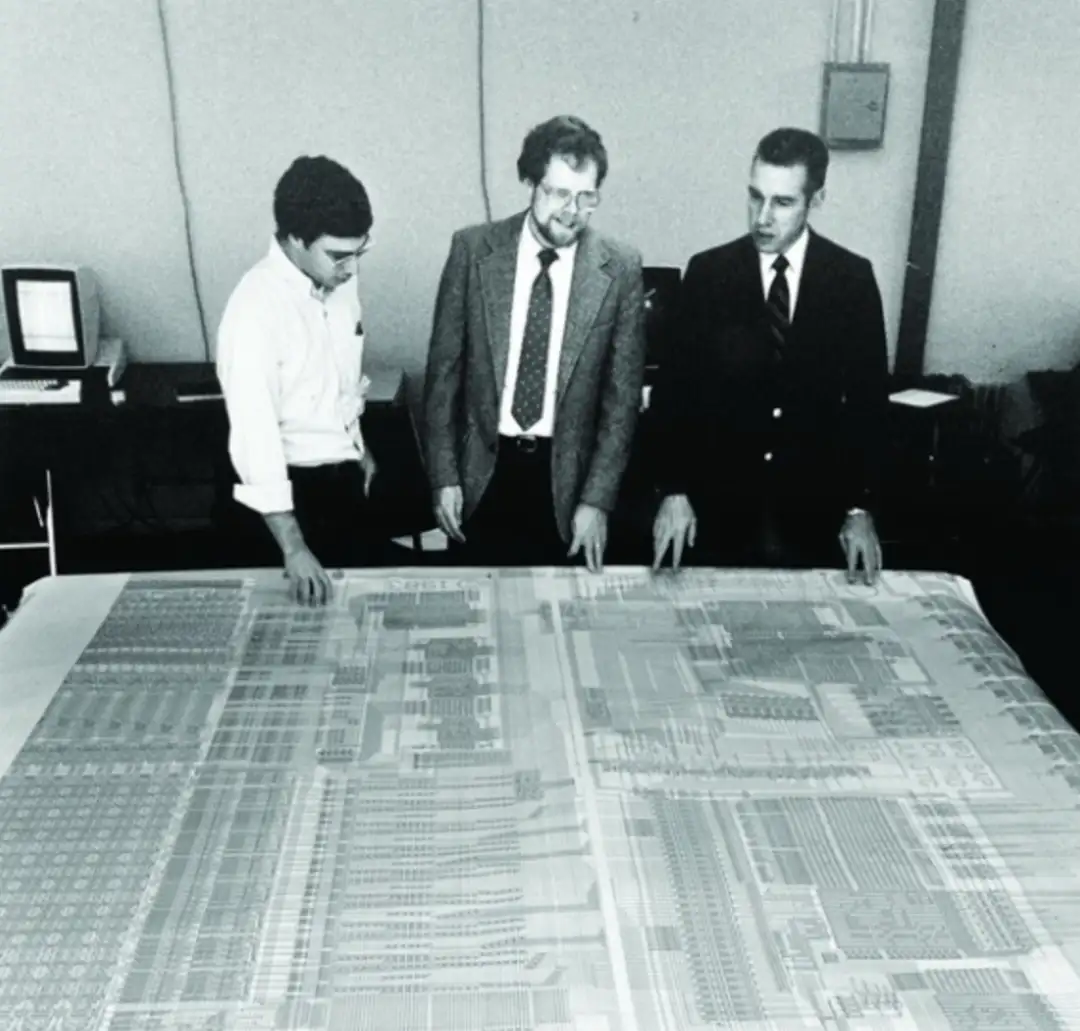

The development of RISC-V has been more tortuous. The RISC architecture was first invented by Turing Award winner and current Google TPU team leader David Patterson in 1971, and has since gone through four generations from RISC-I to RISC-IV, but has never received much attention.

David Patterson (left), 1981

In 2010, Professor Krste Asanovi ć of the University of California, Berkeley decided to develop an open source computer system. x86 was not considered and the cost of Arm was too high. Therefore, David Patterson was hired, and RISC-V was born.

'Open source' and 'modifiable' can almost summarize the essential differences between RISC-V and Arm:

If we use the "martial arts techniques" in martial arts novels as a metaphor for chip architecture, Arm is a martial arts secret code that outsiders can spend money to read, but cannot change casually; RISC-V may just be the practice experience of a martial arts master, which can be continuously revised by various heroes.

The benefits of being modifiable have been difficult to demonstrate in the past, but with the advent of software defined products, the demand for customized chips based on software is becoming increasingly strong, especially in the fields of IoT and automotive. The flexibility of chip architecture can help end manufacturers balance performance and cost.

However, a more practical significance is that RISC-V is open source and free of charge, and is not affiliated with any organization, fundamentally eliminating the possibility of being stuck. In 2015, the Berkeley team announced the establishment of the RISC-V Foundation, putting the principle of neutrality on the table. RISC-V has thus become a hidden backup for developers who are concerned about "architectural hegemony".

Around 2019, as the US sanctions hit, the "spare tire" status of RISC-V quickly became prominent. In addition to Pingtou Ge mentioned earlier, companies in Xiaomi's supply chain such as Huami Technology and Huawei HiSilicon have chip products based on the RISC-V architecture. For a time, RISC-V was in the limelight in China.

Moreover, it is not just Chinese chip companies that are using the RISC-V "spare tire" idea.

Arm is not a 'living bodhisattva'

In August 2022, Arm filed a lawsuit against a major client and brought it to court, triggered by Qualcomm's recent acquisition of Nuvia. The latter was formed by chip engineers from Apple and Google, and after obtaining Arm authorization, developed a series of high-performance CPU cores, which were selected by Qualcomm.

According to Qualcomm's original plan, a customized CPU core based on Nuvia technology called "Oryon" will be launched by the end of this year to compete with Apple's M-series in the PC market on the higher performance Snapdragon SoC platform.

But Arm quit, claiming that Qualcomm's use of Nuvia's technology based on Arm licensing (which stopped in March 2022) infringed on their interests, and demanding that Qualcomm either destroy the chips or provide economic compensation.

There are two types of Arm authorization agreements: the first is the Technology License Agreement (TLA), where customers purchase Arm's IP and can make partial modifications, with Qualcomm's Snapdragon series being a typical representative;

The second type is the Architecture License Agreement (ALA), where customers purchase the Arm instruction set architecture and develop IP and processor cores based on it. A typical representative is Apple, and the conflict center Nuvia also belongs to this category.

The core contradiction of this dispute lies in the fact that Nuvia, before being acquired, had already signed an ALA agreement with Arm and developed an IP based on the Arm architecture. Qualcomm believes that the TLA it has signed with Arm has the right to directly use Nuvia's IP, while Arm believes that Qualcomm needs to obtain its consent in advance (and pay another fee) or directly pay another fee.

This incident has to some extent exposed Arm's vulnerability: although it is a mobile terminal infrastructure, it does not have corresponding "taxation rights".

The status of chip architecture comes more from the "ecosystem": that is, how many downstream customers are willing to adopt this architecture to design chips.

The success of x86 comes from Intel's insistence on compatibility. In the 1980s, Professor Ken Sakamura from the University of Tokyo, as an IT consultant to the Japanese government, proposed an ambitious TRON plan aimed at establishing a Japanese version of the CPU+operating system ecosystem. But unlike Intel's compatibility roadmap, Ken Sakamura believes that Intel sacrifices CPU performance for compatibility and should develop architecture and build an ecosystem from scratch.

Obviously, Intel's path has come to the end. Like TRON, IBM's Power architecture also chose to sacrifice compatibility in pursuit of performance, and was also defeated by Intel.

Intel CEO Otellini delivers silicon wafers to Steve Jobs in 2006

The barrier to "ecology" lies in the "bilateral scale effect": taking Arm as an example, the more chips adopt Arm architecture, the more software developers and users around Arm architecture, and in turn, new chip companies and developers are more inclined towards Arm architecture.

Give a similar example: if there are more users of Meituan, then merchants are more inclined to join Meituan; As the number of merchants increases, users become more inclined to use Meituan. But there is a key premise - Meituan's delivery fees and commissions remain within a reasonable range.

Moreover, most of Meituan's customers are small and medium-sized merchants, while Arm's customers are wealthy and powerful chip giants.

Ultimately, the Arm architecture is more like a representative elected by chip companies through voting. Once Arm starts raising prices or grabbing business (which they are already doing), chip companies have the incentive to vote for a new representative.

The Android system and Nvidia's CUDA are equally dependent on the "ecosystem" as Arm. The former is open source, while the latter is theoretically free, only bound to Nvidia's GPU. At this point, the benefits of RISC-V being free and open-source are evident.

RISC-V, Selected again

Nowadays, the RISC-V Foundation can be described as a gathering of stars. In addition to companies such as Google and IBM that have been involved in the community, there are also Nvidia, Micron, NXP, Western Digital, and Qualcomm, which is most severely persecuted by Arm. The willingness of chip design companies to switch to RISC-V is evident.

Member of RISC-V Foundation; Image source: Semiwiki

Recently, Qualcomm teamed up with several automotive chip giants such as NXP and Infineon to establish a company in Germany with the goal of promoting RISC-V architecture chips. The first target is automotive chips, and the business scope will gradually expand to the mobile and IoT fields.

Another player who is considered likely to determine the development direction of RISC-V is the legendary Jim Keller.

As a living legend in Silicon Valley, Jim Keller led the development of AMD Athlon series processors in the late 1990s, and single handedly put AMD and Intel on an equal footing, causing Intel to abandon its development plan for the 4GHz Pentium 4.

After switching to Apple (PA Semiconductor, acquired by Apple in 2008), Jim Keller created the groundbreaking A4 A-series processor. Later, Jim Keller returned to AMD and led the development of Zen architecture processors, successfully challenging Intel.

In 2020, job hopping activist Jim Keller graduated from Intel and may have stayed in all the big companies in Silicon Valley. Jim Keller then turned to join an unknown Canadian startup company, Tenstorrent.

This company mainly produces AI chips using RISC-V architecture. Jim Keller joined as CTO and became CEO three years later - his first time serving as CEO in his career.

Jim Keller's entry into the game has added a lot of confidence to RISC-V's transition from a spare tire to a regular one, but another company's experience tells us that it's not that easy to get a spare tire on the road.

Lessons from MIPS

Before the emergence of RISC-V, Arm's biggest rival was MIPS.

MIPS, along with Arm and RISC-V, share the same origin and are both RISC architectures mentioned earlier. They were born in the 1980s when PCs began to become popular. At the same time as the development of the Arm architecture by the British company Aikang, former president of Stanford University John LeRoy Hennessy and his team founded MIPS, both of which launched their respective first generation architectures in 1985.

When Aikang was struggling to survive on its only Apple order, MIPS had already tasted the fruits of commercialization. Its third product, R3000, launched in 1988, sold over 100 million and entered the gaming console market through Sony PlayStation. Subsequently, the first 64 bit processor R4000 was released, entering the server and supercomputer markets and becoming the number one threat to x86.

John Hennessy (middle) inspected the layout of MIPS R2000, 1986

However, MIPS continued to decline thereafter, with control changing hands multiple times over the course of more than 20 years. In 2018, Wave Computing, which acquired MIPS from Imagenation, cancelled licensing fees and imitated RISC-V to completely open source the MIPS architecture for free, but it was also difficult to reverse its decline. Finally, Wave Computing announced the termination of development and joined the RISC-V Foundation.

MIPS and Arm both have two authorization modes: IP authorization and architecture authorization, but their approaches differ greatly:

Arm tends to encourage customers to build chips directly using IP without changing the architecture, while MIPS encourages customers to innovate in architecture.

The concept of MIPS seems to give developers maximum freedom, but it invisibly raises the threshold for chip design.

If chip design is compared to building blocks, Arm's solution is to create various components for consumers to assemble on their own; MIPS's solution is to directly provide consumers with various types of wood, allowing them to design their own parts, which is difficult to imagine.

In addition, the determination of architecture is equivalent to establishing a universal rule for hardware and software. Chips, operating systems, software, etc. designed according to this rule can be arranged and combined, and at most some interface modifications can be made to adapt to each other.

MIPS encourages architecture authorization and supports customers to add and modify instructions, which is actually a certain degree of abandonment of universal rules (standardization), resulting in "fragmentation", that is, each link in the industry chain acts independently and cannot achieve "common prosperity". An architecture often changes back and forth to become the Ship of Theseus, making it even more difficult to build an ecosystem.

MIPS and RISC-V are both open-source architectures, while RISC-V is still free. Although the entry threshold for developers has been lowered, this may actually lead to more severe instruction set architecture fragmentation.

Therefore, supporters of the RISC-V camp have been trying to balance customization and standardization:

One approach is to transform 'infinite freedom' into 'limited freedom':

For example, proposing a specification for modifying instruction sets, which requires maximum consideration of software compatibility and encourages hardware developers to modify instructions according to this specification, in order to solve the software and hardware incompatibility problems caused by open source architecture.

A typical example is the Alibaba Pingtou Brother Xuantie C908, which passed the compatibility test set by RISC-V based on its instruction set modification specification. This means that most third-party software developers do not need to worry about software incompatibility issues.

Another approach is to improve the basic instruction set so that developers do not need to make additional modifications:

For example, if RISC-V has a high level of enthusiasm among the developer community for instructions that implement a certain function, the foundation will consider adding a standard version of this instruction to the basic instruction set architecture, so that developers do not need to add instructions separately.

At present, under the intentional guidance of the RISC-V Foundation and members of the giants, both approaches have begun to be implemented, but the obstacles are long.

Hot News

Hot News